Last year, we finished an early version of our Review Unit prototype, which showcased our displays, optics, and primary boards functioning together with our software. Our next major milestone is to deliver a more polished Review Unit (henceforth referred to as Simula's "Polished Review Unit") into the hands of YouTubers. After that, we will release a small early batch of Founders Edition units to our earliest preorderers. And after that, the remainder of our units will be distributed to the rest of our preorderers (in the order they were purchased, with preference for Founders Edition units first).

Below is an overview of the things required to get from here to our first Polished Review Unit, with rough cycle time estimates for each item. (Note that this work is being applied in parallel across our 3 team members).

1 Electrical Engineering Milestones (3 months)

1.1 Finish AR Mode (13-19 days)

First up, we need to finish incorporating our AR Mode infrastructure into our headset. This includes:

-

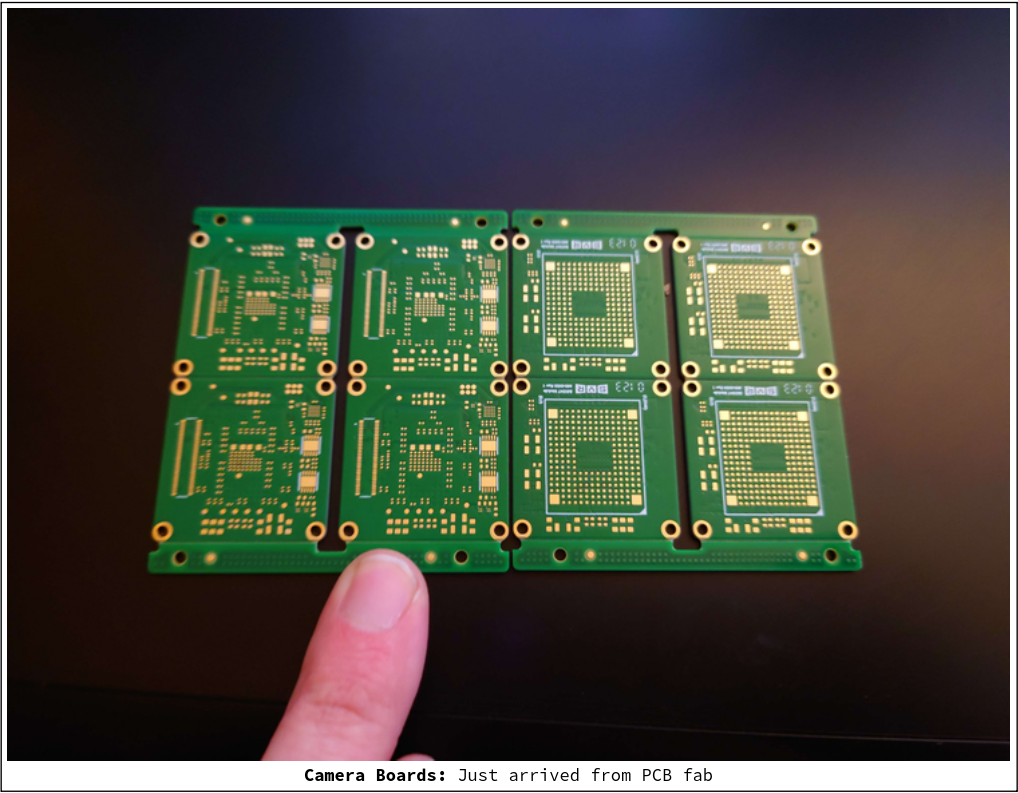

Assemble Camera Boards (10 days). Recall that our Camera Board is the PCB which houses our camera sensor (Sony IMX547), and which transmits its image data to our FPGA for image processing en route to our compute unit. We received the finished batch of Camera Boards we sent to PCB fab, and now need to send them to the PCBA for assembly. Once assembled, we'll run them through some integration testing (optimizing against bandwidth and latency constraints).

-

Fitting (2 day). We'll likely need to iterate on our headset exterior a bit in order to solidify the fit of our new camera hardware.

-

Software polish (1-7 days). Our compositor also needs to be adjusted to accomodate the new camera hardware. This includes things like: adding an adjustable keybind to toggle AR Mode on and off (e.g.

Super + a), adjusting the camera distortion to make sure everything looks suitable, and possibly injecting some performance optimizations to reduce image latency (hopefully this last step won't be needed though).

1.2 Create FPGA Board (2 months)

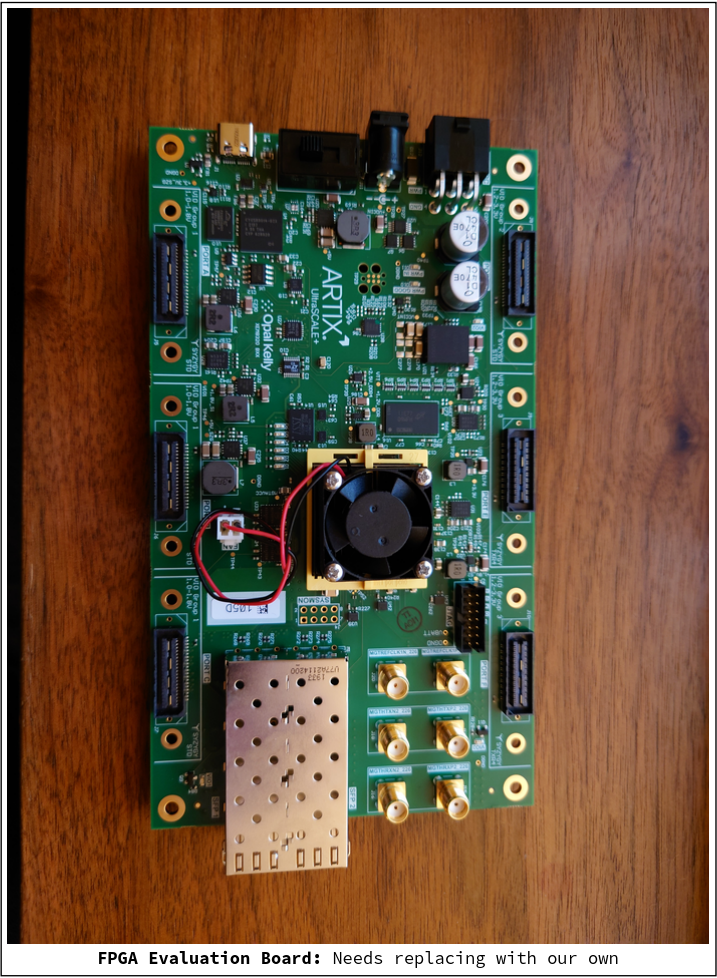

Recall that the Simula One uses an onboard FPGA to efficiently transmit camera data from our image sensors to the host. (We also intend to offload positional & eye tracking to it as well). Right now our (non-polished) Review Unit uses a dangling FPGA evaluation board, which was suitable for testing but now needs to be replaced by our own custom FPGA Board.

We expect to send out a more detailed update on our new FPGA Board soon, but the main requirements for the board are roughly:

- Suitable bandwidth. We need enough bandwidth available to send high-resolution camera images to our host (ideally without compression).

- SLVS-EC protocol. We require SLVS-EC support to route images from the Display Interposer to the FPGA.

- Suitable fit. And of course the FPGA has to be small enough to fit inside our headset exterior.

Will also need some time (roughly 1 week) for the writing + debugging of our FPGA firmware.

More details on our FPGA requirements can be found in our post on Simula One FPGAs.

1.4 Create Carrier Board (2 weeks - 2 months)

Finally, we need to design and implement a Carrier Board which will host our Compute Unit and allow it to snugly dock into the back of our headset. (Presently, our compute unit is just dangling to the side, along with our FPGA evaluation board). Aside from hosting our compute unit, the Carrier Board requirements include:

- Exposing ports. As advertised, we are exposing 1x USB4 (including Thunderbolt 4), 2x USB-C 3.2 Gen 2/DP Alt-Mode, and 2x USB-A 3.2 ports for peripherals.

- Exposing a docking station connector. In order for the Simula One compute pack to attach/detach, we will need for the Carrier Board to expose a port which connects to the back of the headset (essentially allowing the host to connect to the VR displays + other front-facing components).

- Supplying power. The Carrier Board will include an onboard battery to manage and supply power to the headset.

- Thermal regulation. The Carrier Board will contain a fan and other thermal management features.

- Exposing LED lights. The Carrier Board will need indicator lights to display things like power and battery status.

- Buttons. We'll also need some user-friendly buttons which allow the headset to be hibernated, turned on, or turned off.

We will have one more posts on this in the coming weeks, as it's a very important part of our headset. Because we want to get headsets out to people as fast as possible, we are considering outsourcing the development of the Carrier Board to shave off some time.

2 Mechanical Engineering Milestones (3 months)

2.1 Finish IPD Adjustment (5-6 weeks)

-

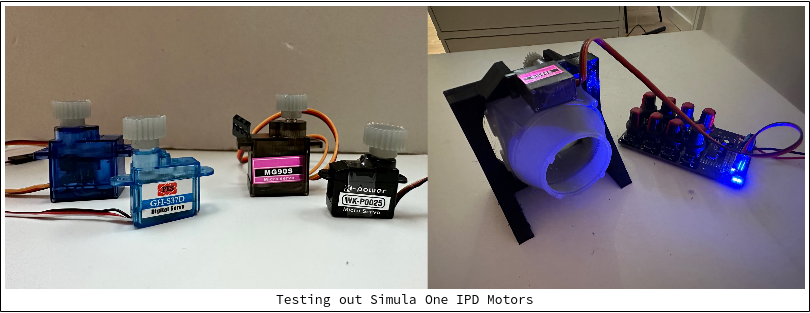

Automatic IPD Adjustment (5 weeks). As we wrote in December, we've been working on adding an Automatic IPD adjustment mechanism to our headset, which requires adding eye sensors and servos. Automatic adjustment is useful for dynamically adjusting IPD over the course of a long VR computing session (as our heads naturally move around and cause the headset to slightly come out of alignment). It also prevents people from incorrectly setting their IPD, and reduces the cognitive setup burden when first putting on the headset.

-

Backup Option: Manual IPD Adjustment (1 week). Though we expect to have automatic adjustment working in our final release, there's a chance we might not be able to get our eye sensors in time for the Polished Review Unit release. In this scenario, we would compromise for a manual IPD solution (in the form of a twist knob or buttons). Since both the automatic and manual solutions require a servo to power the adjustment mechanism anyway, the only thing we'd have to add in this scenario is the time to create a knob that controls the servo.

2.2 Headset Exterior Adjustments (6-8 weeks)

- Internal Frame Iteration (1 week). Our headset exterior needs to be adjusted to fit the Camera Boards & Camera Lenses (also the Eye Sensor & Hand Tracking Units).

- Compute Pack Enclosure (1 week). We need an enclosure to hold our Carrier Board (which holds our host). This is a relatively simple enclosure, but we do need to figure out how to deal with all of the heat.

- Facial Interface Iteration (3-4 weeks). Our Foam Facial Interface needs improvement in its fit & comfort. Since this involves more challenging CAD iteration, we've allotted 3-4 additional weeks for it.

- Polish & Other Things (1-2 weeks). There are also an assortment of smaller things that accumulate into a few more weeks of polish.

3 Software Engineering Polish (1 month)

Finally, we need to apply some polish to our software stack before we are able to deploy Polished Review Units.

This includes:

- Display Stream Compression (DSC) on VXR7200 (1 day). Currently our displays are running with a

60 Hzrefresh rate, but our target is90 - 120 Hz. In order to achieve this, we need to enable DSC, which is a form of "visually lossless" low-latency compression that allows high def displays to reduce their bandwidth demand. Though this is a relatively simple fix, we're still waiting for support from Synaptics. - Hardware acceleration (3 days). Hardware acceleration needs to be enabled on our compute unit (for some reason it's not working; this is a potential monado bug).

- Further rendering improvements (0-10 days). After enabling DSC & hardware acceleration, we might need to apply more rendering improvements to get our compositor running at 90FPS+.

- VR HUD (1 day). Simula's HUD is only visible in "pancake" mode, and needs to be made visible in VR.

- IPD UI (1 day). We would like to add IPD information to Simula's VR HUD as well.

- Boot sequence (5 days). We need to develop our SimulaOS boot sequence (e.g. when the headset turns on, our compositor is launched alongside some other helpers). We are using NixOS as the basis of our default fork. We also want to provide a default bluetooth mouse & keyboard which is detected and enabled.

4 Total Estimate: 3 months

Some notes about the above time estimates:

- We have a 3 person team, so are able to parallelize the above tasks (largely along the lines of Mechanical/Software/Electrical engineering tasks). This gets us to roughly 3 months of cycle time before we have Polished Review Units.

- Just to emphasize what we said above: we are intending to outsource the development of our Carrier Board. (If we are unable to do this, it could add another ~1.5 months of cycle time).

Onward towards the New Year.