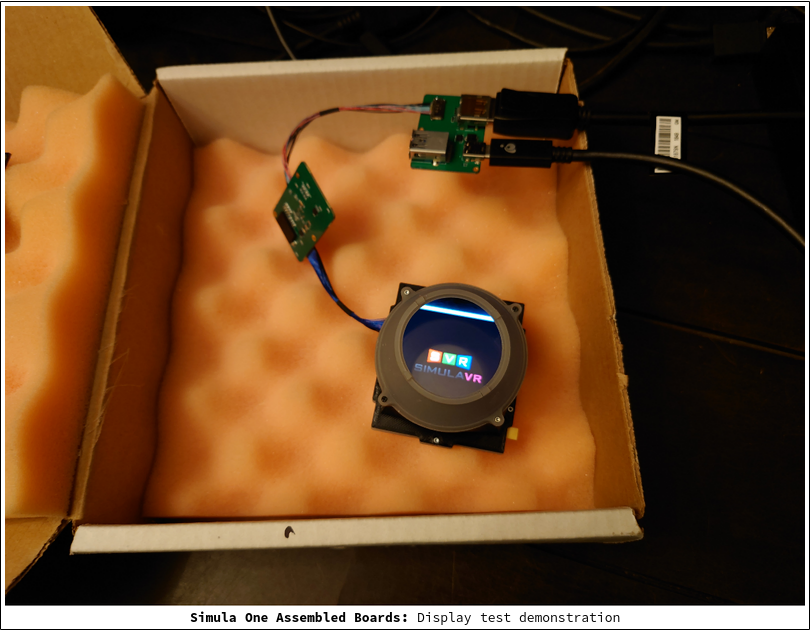

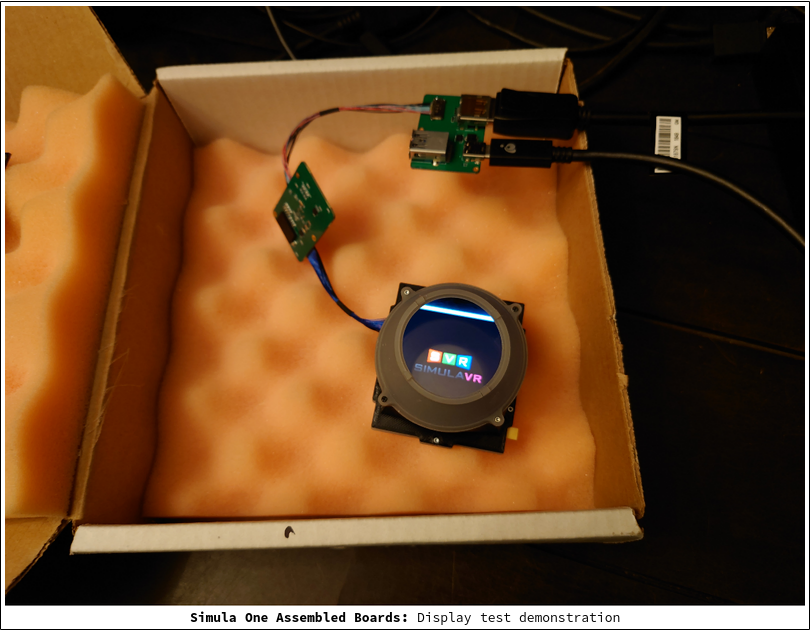

We're pleased to confirm that our newly assembled boards are integrated:

Caveats: there were some minor (but fixable) issues we've had to sort through, with one fix unfortunately requiring our Display Interposers to be respun at our PCBA. This has added another week or so of lead time to our review unit timeline. Details below.

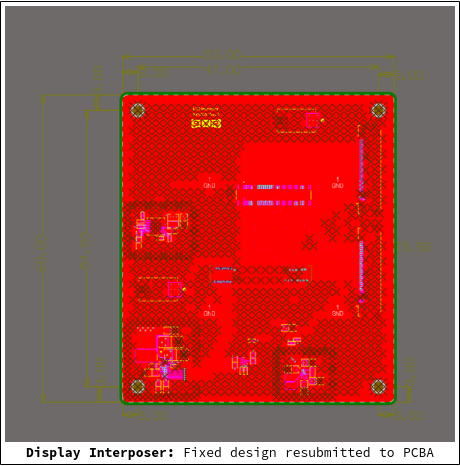

Our fixed Display Interposer design has been resubmitted to PCBA

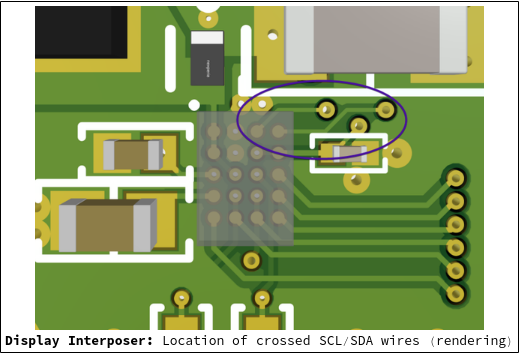

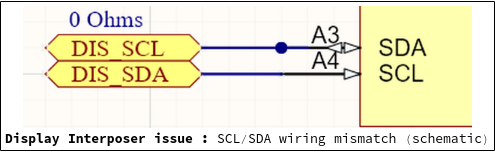

First, our Display Interposer unfortunately had a wiring mismatch between the SCL (Serial Clock signal) and SDA (Serial Data signal) on its i2c bus.

Schematically the mismatch looks like this:

We submitted an updated design to our PCBA earlier this week (on 08/07), with a ~2 week lead time:

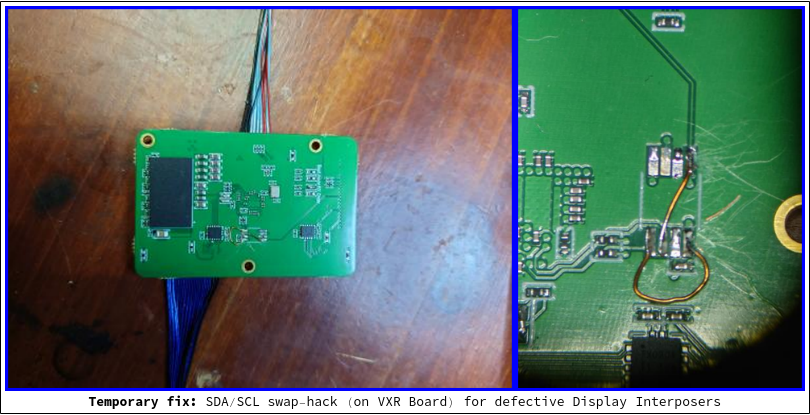

It's a shame we have to wait for a board respin just for this, but unfortunately it was impossible to fix this ad-hoc. For now we were able to hack around this by removing a mux chip on our VXR board and swapping SDA/SCL.

Aside from this, the only other issue for this board is at the firmware level: for some reason we are unable to write to the interposer's i2c bus on display initialization. The Synaptics firmware i2c.write command isn't working, and we haven't figured out why.

We're currently waiting on assistance from Synaptics, although a manual workaround via their debug tool is possible. If this is not fixable on the VXR for some reason, we'll have a microcontroller write to the bus.

VXR MIPI issue

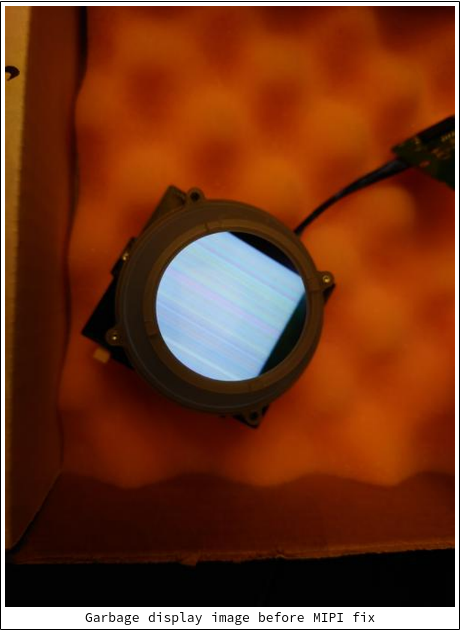

The only other issues were with our VXR configuration. After getting around I2C issue and turning on the backlight, we were met with a corrupted image:

It turns out we entered the wrong lane configuration into the VXR for MIPI PHY1. To explain, each of the displays accepts 2 4-lane MIPI D-PHY links. For ease of routing, the VXR supports remapping the physical lanes internally (so you can just route straight lines), and the lane order for PHY1 was "[VXR lane] 0 to [Display lane] 3, 1 to 0, 2 to 1, 3 to 2" instead of "0 to 1, 1 to 2, 2 to 3, 3 to 0" (or "0x93" instead of "0x39" in the configuration file). After fixing this, we were able to finally get images sent to our displays:

Things remaining for review units

We've been working on our cameras while waiting for the upgraded Display Interposer. When the boards arrive, these will be the things left to do:

- Test updated Display Interposers

- Print new holders for Display Interposers

- Print a holder for the VXR board

- Fix the

i2c.writeissue described above - Assemble lenses

We're now targeting end of August for our finished Review Unit.